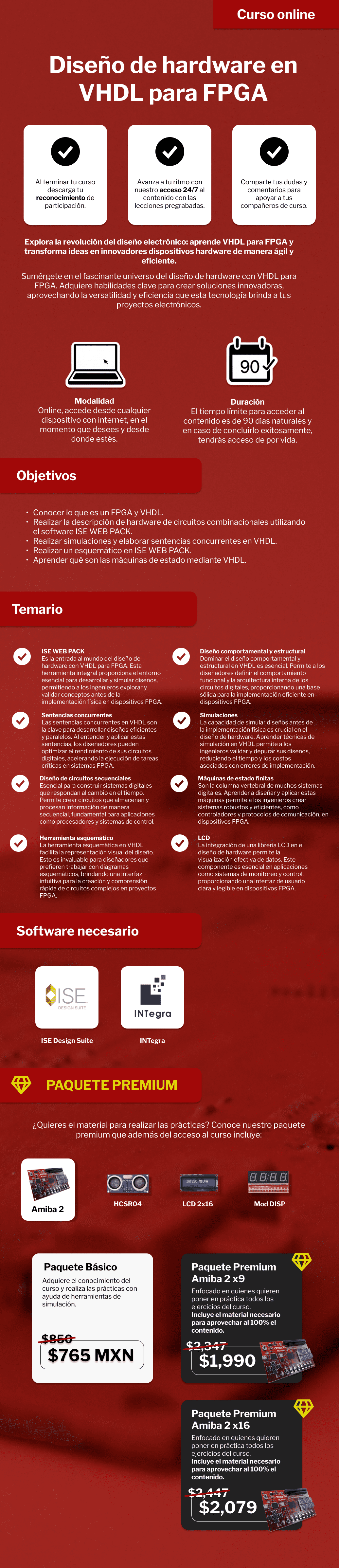

Diseño de hardware en VHDL para FPGA

Acerca de este curso

Contenido del curso

Tema 1. Introducción

-

Tema 1. Introducción

01:21 -

1.1. ¿Qué hay en el curso?

01:50 -

1.2. Estructura interna de un FPGA

03:16 -

1.3. ¿Qué es VHDL?

01:55 -

Cuestionario 1. ¿Qué son los FPGAs?

Tema 2. ISE Design Suite e INTegra

Tema 3. Simulación

Tema 4. Diseño comportamental y estructural

Tema 5. Sentencias concurrentes

Tema 6. Diseño de circuitos secuenciales

Tema 7. Máquinas de estado finitas

Tema 8. Uso de la herramienta esquemático

Tema 9. Manejo de librerías

Banco de ejercicios A

Banco de ejercicios B

Proyecto Final

Examen final

Valoraciones y reseñas de estudiantes

Aún no hay reseñas.